TANG-NANO: Unterschied zwischen den Versionen

Andi (Diskussion | Beiträge) |

Andi (Diskussion | Beiträge) |

||

| Zeile 66: | Zeile 66: | ||

Datei:Gowin Dual Purpose Pins Settings.png|Gowin Dual Purpose Pins Settings | Datei:Gowin Dual Purpose Pins Settings.png|Gowin Dual Purpose Pins Settings | ||

Datei:Gowin Synthesis Settings.png|Gowin Synthesis Settings | Datei:Gowin Synthesis Settings.png|Gowin Synthesis Settings | ||

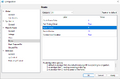

Datei:Place.png|mini|Place algorithm options | |||

Datei:Route.png|mini|Route algorithm options | |||

</gallery> | </gallery> | ||

oder alternativ, wenn nur ein fertiges FPGA-File programmiert werden soll: | oder alternativ, wenn nur ein fertiges FPGA-File programmiert werden soll: | ||

Version vom 17. August 2025, 19:54 Uhr

Beschreibung

Beim Tang-Nano-20k handelt es sich um ein preisgünstiges, jedoch leistungsfähiges FPGA-Board mit welchem aktuell einige verschiedene Karten emuliert werden können. Das interessante daran ist dass es einen (relativ großen) FPGA (~20k LUT) mit einem SD-RAM mit 64MBit (8 MByte) kombiniert. Dadurch ist man in der Lage komplette Systeme (CPU, Peripherals + Speicher) darin unter zu bringen.

Für nähere Informationen zum Tang-Nano-20k Board siehe: https://wiki.sipeed.com/hardware/en/tang/tang-nano-20k/nano-20k.html

Schaltplan: Schaltplan

FPGA-Files:

Sourcecode:

- GDP-FPGA Source auf Github

- GDP64-FPGA (Bus-Slave) Gowin Workspace

- 68k-SOC (Bus-Master) Gowin Workspace

- Z80-SOC (Bus-Master) Gowin Workspace

Emulierte Karten (Stand 08.2025):

- GDP64HS-FPGA inkl. Farberweiterung mit 256 Farben mit HDMI-Ausgang

- PS/2 Key

- PS/2 Mouse

- Sound

- SD-Card (SPI, SDIO)

- Ser

- Timer (interruptfähig)

- Komplettes Z80 System on chip (SOC) mit 8MHz Z80 CPU, 1MB RAM, Peripherals lt. Liste oben, ext. I/O-Bus

ROMS: - Flomon 4.2 oder GP2019 - Zeat - Basic - Gosi - Grundprogramm

- Komplettes 68k System on chip (SOC) mit 10MHz 68000 CPU (16-bit), 2MB RAM, Peripherals lt. Liste oben, ext. I/O-Bus

ROM: GP7.10R5

Das Tang-Nano-20k kann als Bus-Slave betrieben werden (mit einer externen CPU) als z.B. GDP64HS oder auch als komplettes "System on Chip" (Bus-Master) mit Z80 oder 68000 CPU und internen RAM.

Dabei können über compile-time Switches die im FPGA-File enthaltenen Peripherals ein/ausgeschaltet werden (true = enthalten). Diese Switches befinden sich in der jeweiligen Toplevel-Unit. Wenn der Gowin Workspace im GOWIN FPGA Designer geöffnet ist dann kann die Toplevel-Unit einfach durch Doppelclick auf das oberste file in der Hierarchy-Ansicht geöffnet werden.

Switches für GDP-FPGA (Bus-Slave)

Die Farberweiterung der GDP64HS-FPGA kann ebenfalls mittels Switch (im globalen Package) abgeschaltet werden. Dann verhält sie sich zu 100% wie eine GDP64HS

Switch zum abschalten der Farberweiterung bei der GDP-FPGA

Switch zum abschalten der Farberweiterung bei Z80 UND 68k SOC

Benötigte Software:

- Gowin Education (ab Version V1.9.10.03, Gowin V1.9.11.03 Education (Windows x64))

Damit kann der VHDL-Source synthetisiert (übersetzt) werden und ein FPGA file zur Programmierung des Tang-Nano erzeugt werden.

Folgende Settings in der Gowin Software müssen vorher noch umgestellt werden (Project - Configuration):

oder alternativ, wenn nur ein fertiges FPGA-File programmiert werden soll:

- GOWIN Programmer (ab Version V1.9.10.03, GOWIN Programmer V1.9.11.02 (Windows))

Übersetzen des Sourcecodes:

Ein FPGA-file zur Programmierung des Tang-Nano-20k Boards kann mittels click auf "Run All" Button erzeugt werden.

Programmierung:

Zum programmieren des Tang-Nano-20k muss der Programmer gestartet werden. Wenn dieser aus der Gowin FPGA Designer Software gestartet wird ist das richtige FPGA-File schon vorausgewählt. Um ein FPGA-File permanent auf dem Tang-Nano-20k zu speichern (im Flash) muss als Operation "exFlash Erase,Programm thru GAO-Bridge" ausgewählt werden - siehe Bilder unten.