MEM960k

Ziel diese Projektes war es mit minimalem Bauteileaufwand mehr RAM für meinem 68k NKC realisieren.

Ideen:

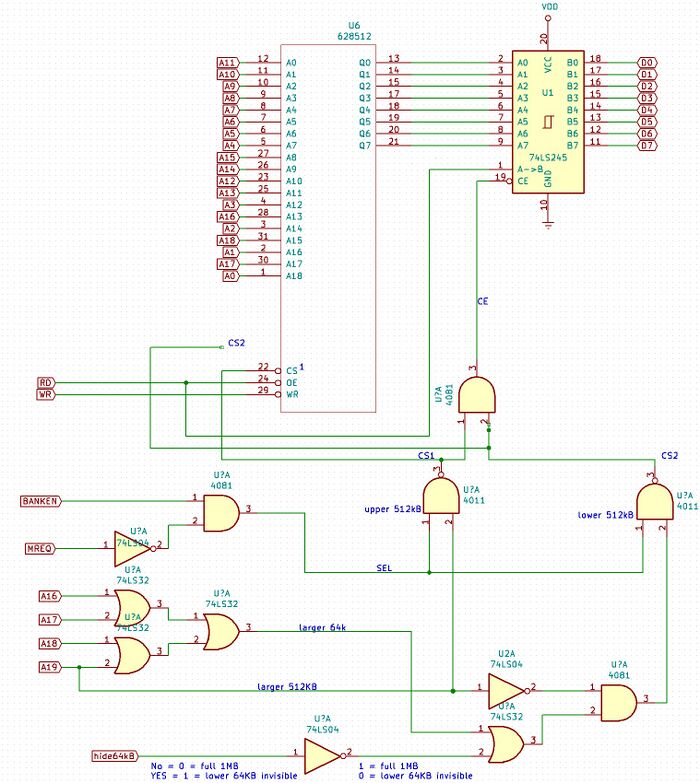

- Adressdekodierung und Generierung von /CS und /CE übernimmt ein GAL

- Stacking der RAM chips [[1]]

- Durch eine kombinierte Buchsen/Steckerleiste verbraucht die Karte keinen Steckplatz auf dem BUS. Eine beliebige Karte kann auf der MEM960k stecken.

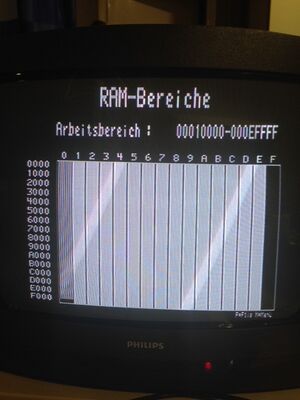

- 1MB, mit der Möglichkeit über einen Jumper die unteren 64k ($0000 - $FFFF) auszublenden. Das ist praktisch um das Grundprogramm auf EPROMs auf einer ROA64 zu haben. 1MB-64k=960k, daher der Name.

Testen

Getetset/entwickelt habe ich die Schaltung mit 'Tina' [[2]]. Ohne Simulation wäre diese Projekt gescheitert. Als totaler Anfänger hat das Simulieren der Schaltung riesigen Spass gemacht - ein wunderbares Logikrätsel bis alles so funktionierte wie es soll.

Mit 'Tina' kann man interaktiv, mit einer Kaffetasse in der Hand, der Katze auf dem Schoss und Jazzmusik im Hintergrund an einem Sonntagnachmittag alles in Ruhe ausprobieren - bis es endlich klappt, oder die Frau einen Spaziergang machen will.

Die Schaltung in der Realität mit so vielen Gattern so aufzubauen führt zu einem 'TTL-Grab', es kann einiges vereinfacht werden, was zwar zu weniger Gattern führt, aber in der Regel lässt sich die Funktion von optimierten Schaltungen nicht mehr so einfach nachvollziehen. Die Optimierung überlasse ich daher lieber schlauen Algorithmen, im nächten Schritt:

Die Logikgatter wurden als GAL realisiert, dazu habe ich mir einen China-GAL-Brenner und ein Handvoll 16V8 GALs von eBay besorgt. Gebrannt wir ein JED file, das kann man zB mit WinCUPL [[3]] erzeugen. Die Logikgatter vom Schaltplan in Equations umzusetzen bekommt man schnell hin. Hier das WinCUPL file aus dem ein JED file erzeugt wird:

/* *************** INPUT PINS *********************/

PIN 2 = MREQ; /* */

PIN 4 = A16; /* */

PIN 5 = A17; /* */

PIN 6 = A18; /* */

PIN 7 = A19; /* */

PIN 3 = BANKEN;

PIN 11 = hide64kB; /*YES = 1 = lower 64kB OFF */

/* *************** OUTPUT PINS *********************/

PIN 19 = CSlow; /*Lower 512k */

PIN 18 = CSup; /*Upper 512k */

PIN 17 = CE; /*CE for 74LS245*/

/* *************** EQUATIONS *********************/

SEL = BANKEN & !MREQ;

CS1 = !(SEL & A19);

CS2 = !(SEL & (!A19 & ((A16 # A17 # A18 # A19) # !hide64kB)));

CSlow = CS1;

CSup = CS2;

CE = CS1 & CS2;

/* ****************** END ************************/

Das GAL habe ich dann erst mal auf Herz-und-Nieren getestet. Alles ok - und mein Hobby-Labor hat eine weitere Technologie erschlossen...GALs !! OMG, davon konnte ich 1983 nur träumen!

Aufbau

Ich habe die Karte in WireWrap Technik aufgebaut, das geht super schnell (naja..), ist zuverlässig (NASA Apollo Steueungscomputer war in WireWrap), stinkt nicht und kann nach belieben verändert werden - ideal ! WireWrap[4] und [[Hackaday][5]]

Eine Besonderheit die den Aufbau erheblich vereinfacht: Die Reihenfolge der Adressleitungen zum RAM chip spielt keine Rolle, es muss also nicht BUS A5 an Chip A5 - man kann die Adressleitungen so verlegen wie es mechnaisch am günstigsten ist; dasselbe gilt für die Datenleitungen.

Beim GAL kann man die Pins frei konfigurieren sodass sich insgesamt eine sehr einfache Verkabelung ergibt. Falls man doch eine Platine wünscht, kommt man wahrscheinlich mit einem einseitigen Layout aus (ich werde das mal spasseshalber ausprobieren).

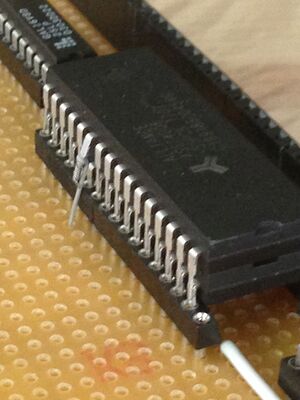

Das RAM-stacking ist natürlich eine wilde "Technologie", funktioniert aber wunderbar. Erster Testlauf war mit 512k dann einfach ein weiteres RAM aufgesteckt (noch nicht einmal gelötet), /CS verkabelt - und voilà -1MB!

Stückliste:

1 x 74LS245

1 x GAL16V8

2 x 512kb SRAM zB.628512

Erweiterung

16bit Version: zweiten '245 und zweiten Ramstack hinzu und über den BUS CPU Steckplatz die zusätzlichen Adressleitungen anzapfen. Die CPU steckt dann auf der MEM960k (die zu einer MEM1920k geworden ist).

Dies ist eine BUS-Steckplatz schonende Speicherlösung für 68000 und 68020.

Sonstiges

- ist es ratsam die Adressleitungen zu puffern ?

- funktioniert die Karte in einem Z80 System ?

- noch nicht mit 68000 und 68020 getestet